پیاده سازی سخت افزاری سبک وزن الگوریتم های رمزنگاری

فایل تحقیق “پیاده سازی سخت افزاری سبک وزن”

تعداد صفحات: 18 صفحه

اهم سرفصل ها:

- بده بستان بین امنیت، هزینه و کارآیی در طراحی و پیاده سازی الگوریتم

- سه گام مهم در مسیر طراحی و پیاده سازی سبک وزن

- مهمترین پارامترهایی که در ارزیابی سخت افزاری (بخصوص سبک وزن)

طراحی سخت افزاری بهینه - انتخاب بهینه تراشه و فناوری

- مراجع

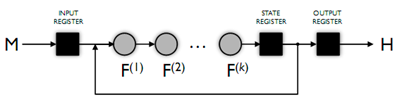

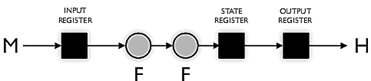

در ابتدا کلیات پیاده سازی سخت افزاری سبک وزن بیان می شوند. در بخش دوم ابتدا پارامترهای مهم ارزیابی سختافزاری (هر الگوریتم کنترلی-رمزنگاری-پردازشی) بیان میشود. در بخش سوم، روشهای مهم بهینهسازی طراحی بیان میشوند. در بخش چهارم خواهیم دید که انتخاب فناوری، حافظه و تراشه نقش بسزایی در ناحیه سختافزاری دارند.

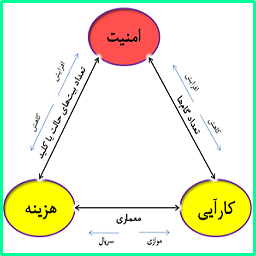

هنگامی که صحبت از رمزنگاری می شود، همواره با توجه به کاربرد مورد نظر با سه مسئله اساسی امنیت، هزینه[1] و کارآیی[2] روبرو هستیم. پس از تحلیل و بررسی کاربرد مورد نظر، سطح امنیتی لازم در مقابل حملات ممکن مشخص میشود. طراحی الگوریتم در مرحله اول باید طوری باشد که امنیت لازم را تأمین کند. به عنوان مثال در توابع چکیده ساز با سه پارامتر امنیتی تصادم، پیش تصویر (دوم) و تصادفی بودن روبرو هستیم که بسته به کاربرد مورد نظر باید تأمین شوند. پس از مشخص شدن سطح امنیت و جزئیات پیرامون آن و با توجه به اینکه چه هزینه هایی، شامل ناحیه سخت افزاری[3] و توان مصرفی[4]، در دسترس بوده و یا باید در قبال حل مسئله اول پرداخت، نوع طراحی و سخت افزار مناسب مشخص می شود. کارآیی که معمولاً با دو پارامتر فرکانس و تعداد پالس زمانی لازم جهت اجرای الگوریتم، مشخص می شود نیز با امنیت و هزینه در ارتباط است. بنابراین سه معیار امنیت، هزینه و کارآیی (برونداد) همواره با یکدیگر در بده بستان هستند (شکل 1) و بدست آوردن نقطه بهینه، کار بسیار دشواری است. از طرفی هنگام انتخاب سخت افزار نیز باید به نوع معماری، نوع طراحی و نوع فناوری توجه کرد. همانطور که خواهیم دید، انتخاب سخت افزار نیز میتواند نقش چشمگیری در تعیین هزینه داشته باشد.

جدول 1: معادل گیت عناصر سختافزاری [4]

| عملگر منطقی | هزینه ناحیه در ASIC |

| NAND(x,y) | 1.00 GE |

| AND(x,y) | 1.25 GE |

| OR(x,y) | 1.25 GE |

| XOR(x,y) | 2.25 GE |

| MUX(x,y;s) | 2.50 GE |

| AND(x,y,z) | 1.50 GE |

| MAJ(x,y,z) | 2.25 GE |

| XOR(x,y,z) | 4.00 GE |

| 1 bit (state or flip-flop) | 5.50-7.50 GE |

جدول 2: توان برخی فناوری ASICها با توجه به کتابخانه های استاندارد تجاری [1]

| فناوری | توان () | چگالی گیت () |

| 180 nm | 00/15 | 125 |

| 130 nm | 00/10 | 206 |

| 90 nm | 00/7 | 403 |

| 65 nm | 68/5 | 800 |

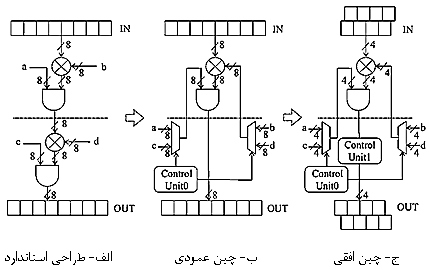

شکل 6: روش بازشدگی [6]

شکل 7: الف-اعمال روش 2-بازشدگی و ب- اعمال باز زمانی روی (الف) [6]